AD1955解码器设计流程图

- 时间:2015年04月02日 15:12:36 来源:魔法猪系统重装大师官网 人气:13520

继CS439之后,又设计了这款AD1955的解码器,AD1955的综合性能要优于CS4398,当然由低通模拟单元造成的成本也会大幅增加。

本DAC设计中,数字接收单元采用CS8416,电源部分则认真挑选了普通三端稳压器,保证电压配对与误差,电压转换则采用OPA627BP运放,单颗运放价值160多人民币,想不好声都难,电压转换都用了OPA627BP,低通滤波自然采用与之配套的OPA637BP,6颗运放都上千了,“俄滴神啊”,不知大家有何感想了。本次设计,外观上采用了与上款439dac相同的机械外观尺寸,好处就是一旦做了外壳,可以通用。以下就整体设计展开详细描述。

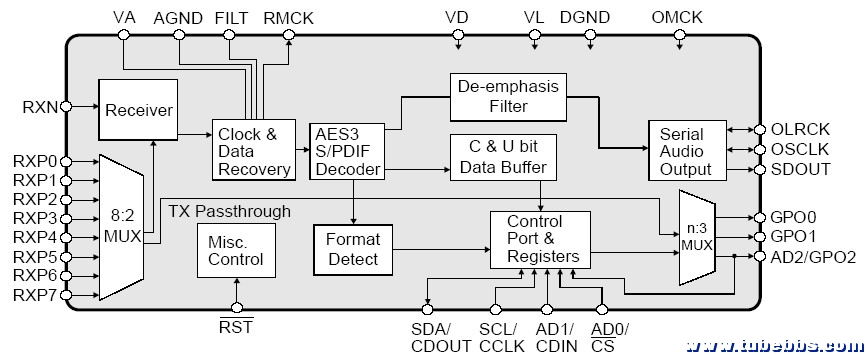

CS8416内部功能图如下:

CS8416是CIRRUS LOGIC近期产品之一,是192KHZ数字音频接收芯片,工作电压为3.3V,兼容5V TTL逻辑电平,与其它同类产品比,内部还整合了8通道模拟切换开关,十分方便进行多通道输入选择,简化外围电路设计。CS8416的工作坊式分为软件控制模式和硬件控制模式,在软件控制模式下需要借助外部MCU对CS8416内部寄存器进行读写操作才能完成控制,会有较为复杂的外围设计以及一定的技术难度,对于我们业余玩家来说意义不是很大,所以笔者在本设计中选择CS8416为硬件控制模式,硬件模式下数据流程如下:

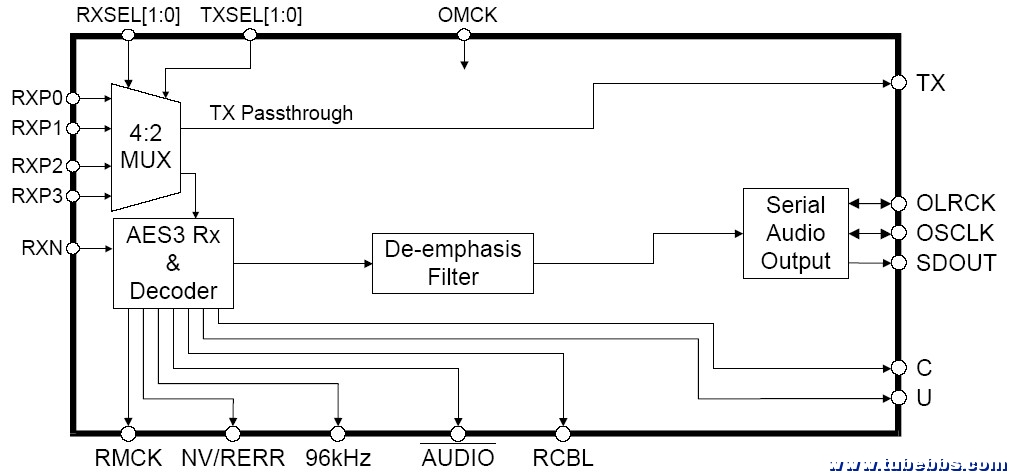

从图二中可以看出,在硬件控制模式下,CS8416的使用更加简洁,外部输入通道减少为4个,它的各种工作模式则由相应得引脚的系统复位期间的逻辑电平来决定,硬件控制模式下的各引脚定义见表一:

从表一可以看出,我们首先必须把SDOUT管脚接地才能为硬件控制模式;由于笔者为单一芯片应用设计,所以RCBL自然选择为拉高----首选模式;音频格式设定1和0就是我们常说的IIS数据的选择控制了,对于CS8416,“设定1”必须接地,“设定0”则必须拉高,这样CS8416的串行音频数据输出端口就可以获得我们所需要IIS 24bit数据流了;U接地选择256Fs;TX接地;96KHZ接地;NV/RERR接地。至此,CS8416的工作方式就完全确定啦。

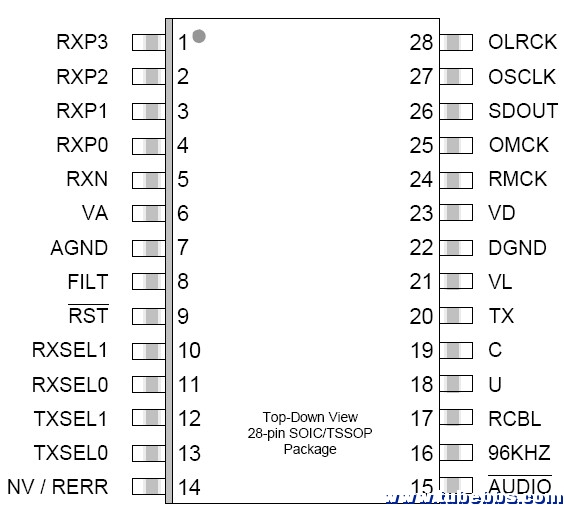

图三所示为CS8416工作于硬件模式的引脚定义图,但是他们在实际的使用还是有一定的要求的,下面对各引脚作简单的说明:

1脚:输入通道3

2脚:输入通道2

3脚:输入通道1

4脚:输入通道0

这4个输入通道的中不使用的通道可以悬浮或者直接接地处理,通道的选择由10脚和11脚的逻辑电平控制。可以输入单端信号或者差分信号。输入差分信号的时候需要与5脚配合。

5脚:差分输入的负端。当采用单端输入的时候,该引脚通过一个耦合电容接地。

6脚:VA。该脚为芯片内波模拟电路供电电源,该电源的精度则直接影响到时基抖动,对输出信号的稳定性造成影响。电压要求为3.3V

7脚:AGND。电源VA的模拟地。

8脚:锁相环滤波器接入脚。为了保证稳定性,滤波器RC网络的接地端一定要与7脚AGND尽可能短。

9脚:复位输入脚。低电平有效。

10脚:数据格式设定1

11脚:数据格式设定0

12脚:TX输出与RX通道直通选择设定1

13脚:TX输出与RX通道直通选择设定0

当TX不被使用的时候,请将TX通道设定到不被用到的输入通道上。

14脚:接收数据不能识别指示

15脚:音频数据流指示。

16脚:96KHZ采样频率检测。当采样频率小于等于48KHZ的时候,输出低电平;大于88.1KHZ的时候输出高电平。

17脚:数据接收器状态输出

18脚:U状态输出

19脚:C状态输出

20脚:TX输出引脚。

21脚:内部逻辑电路电源输入。电压为3.3V或者5V。

22脚:内部逻辑门电路电源地与内部音频数据处理单元电源地。

23脚:内部音频数据处理单元电源输入。电压为3.3V。

24脚:主时钟输出。

25脚:外部时钟输入。

26脚:串行音频数据流数据位输出。

27脚:串行音频数据流数据的位时钟输出。

28脚:串行音频数据流左右通道分割时钟输出。

CS8416无论工作与硬件控制还是软件控制模式下,都可以通过串行通讯口与内部寄存器进行读操作,笔者虽没有在电路中设计有MCU,但是在电路中保留了IIC串行通讯接口,方便以后加装MCU实现数据显示功能。有关内部寄存器组这里不再详述,有兴趣的同好可以自己翻阅CS8416数据手册去研究。

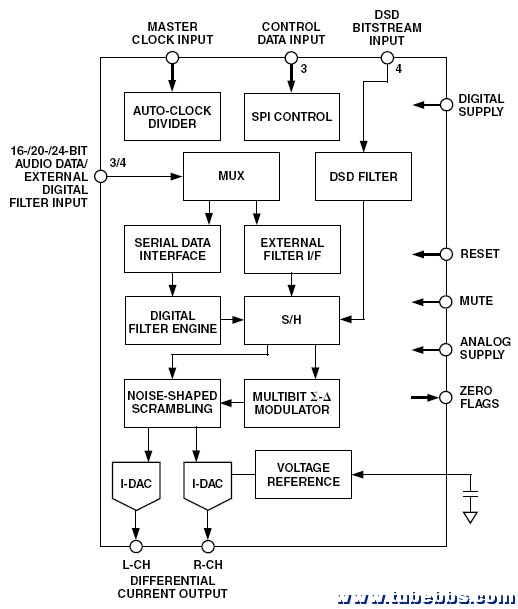

本次设计的核心芯片是ANALOG公司出品的高性能多位西格玛-德尔塔转换器件AD1955,该芯片为单电源供电,支持采样频率达192khz ,在48khz采样频率应用下信噪比可达120DB,内部整合有8倍过采样频率数字滤波器。方便设计者进行电路设计,并以较低的代价即可构成高性能的应用。在其他同类芯片中,还有CS4398,PCM1798等也具有各自的特点,但是纵观ad1955的模拟转换器的电流输出能力,AD1955居然达到8.64ma P-P值,并且还需要设置有3.24ma的偏置输入电流保证,我们在实际应用往往容易发现一点,性能的提升必然要以功耗的付出做代价,效率的提升必然以工艺的改善为基础。

AD1955 DA转换器的内部功能块结构图如图四,从结构图就可以发现该芯片的应用设计极为简单明了,并无太多的逻辑设定。和CS8416一样,该芯片同样可以采用外部MCU控制使其工作于软件控制模式,但是该芯片的特点就是当没有外部MCU来写内部寄存器的时候,只要数据格式符合内部寄存器的初始默认值就可以正常工作,很方便设计者构成单片应用设计。对于AD1955的深层应用设计,笔者在这里不再描述。

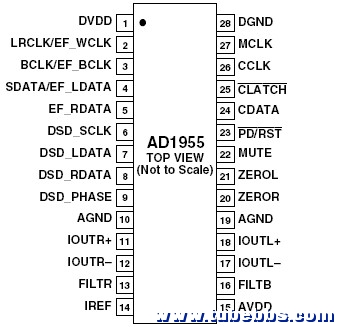

AD1955的引脚图如图五所示,对于不用的输入引脚(DSD数据输入端口),直接接地处理;不用的输出引脚(左右通道0标志输出引脚),悬浮处理;串行通讯口用上拉电阻接到电源即可。